# LABORATORY MANUAL FOR THE COURSE

**INTEGRATED CIRCUITS LABORATORY (ECE 318)-R15**

# **Prepared By:**

**Checked By:**

Mr.N.Ramkumar,AP/ECE Mr.V.Sateesh,AP/ECE

Signature of the HOD:

ANIL NEERUKONDA INSTITUTE OF TECHNOLOGY & SCIENCES (Affiliated to Andhra University) Sangivalasa-531162, Bheemunipatnam Mandal, Visakhapatnam Dt. Phone: 08933- 225084,226395

# **INTEGRATED CIRCUITS LABORATORY**

| Credits:2          |

|--------------------|

| Sessional Marks:50 |

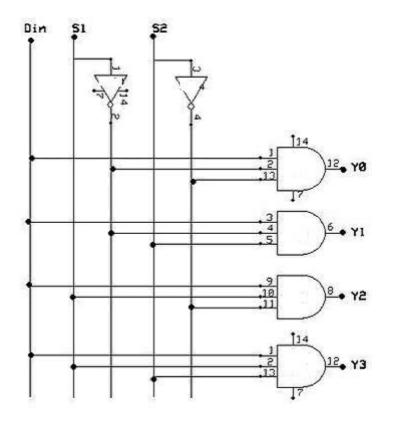

| End Exam Marks:50  |

|                    |

#### **Prerequisites:**

Digital Electronics, Integrated Circuits and Applications

# **COURSE OBJECTIVES**

- > To understand the non-linear applications of operational amplifiers(741)

- > To familiarize with theory and applications of 555 timers.

- > To design and construct waveform generation circuits using Op-Amp

- > To design multivibrator circuits using IC555

- > To design and analyze combinational and sequential logic circuits

# COURSE OUTCOMES

At the end of the course student will be able to

- 1. Design the circuits using op-amps for various applications like Schmitt Trigger, Precision Rectifier, Comparators and three terminal IC 78XX regulator.

- 2. Design active filters for the given specifications and obtain their frequency response characteristics.

- 3. Design and analyze multivibrator circuits using op-amp and 555Timer

- 4. Design and analyze various combinational circuits like multiplexers, and de-multiplexers, binary adder, subractor, etc

- 5. Design and analyze various sequential circuits like flip-flops, counters etc

### Mapping of Course Outcomes with Program Outcomes:

|    |   |   | РО |   |   |   |   | PSO |   |   |    |    |    |   |   |   |

|----|---|---|----|---|---|---|---|-----|---|---|----|----|----|---|---|---|

| _  |   | 1 | 2  | 3 | 4 | 5 | 6 | 7   | 8 | 9 | 10 | 11 | 12 | 1 | 2 | 3 |

|    | 1 | 2 | 1  | 2 | 2 | 2 | - | -   | - | 2 | 1  | 2  | 1  | 3 | 3 | 2 |

|    | 2 | 2 | 2  | 1 | 2 | 2 | - | -   | - | 2 | 1  | 2  | 1  | 2 | 2 | 2 |

| CO | 3 | 2 | 2  | 1 | 2 | 2 | - | -   | - | 2 | 1  | 2  | 1  | 2 | 2 | 2 |

|    | 4 | 2 | 2  | 2 | 1 | 2 | - | -   | - | 2 | 1  | 2  | 1  | 2 | 2 | 2 |

|    | 5 | 2 | 2  | 3 | 1 | 2 | - | -   | - | 2 | 1  | 2  | 1  | 2 | 2 | 2 |

### 3: high correlation, 2: medium correlation, 1: low correlation

### **PROGRAM OUTCOMES**

- 1. **Engineering knowledge:** Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialisation for the solution of complex engineering problems.

- 2. **Problem analysis:** Identify, formulate, research literature, and analyse complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

- 3. **Design/development of solutions:** Design solutions for complex engineering problems and design system components or processes that meet the specified needs.

- 4. **Conduct investigations of complex problems:** An ability to design and conduct scientific and engineering experiments, as well as to analyze and interpret data to provide valid conclusions

- 5. **Modern tool usage:** Ability to apply appropriate techniques, modern engineering and IT tools, to engineering problems.

- 6. **The engineer and society:** An ability to apply reasoning to assess societal, safety, health and cultural issues and the consequent responsibilities relevant to the professional engineering practice

- 7. Environment and sustainability: An ability to understand the impact of professional engineering solutions in societal and environmental contexts

- 8. **Ethics:** Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- 9. **Individual and team work:** Ability to function effectively as an individual, and as a member or leader in a team, and in multidisciplinary tasks.

- 10. **Communication:** Ability to communicate effectively on engineering activities with the engineering community such as, being able to comprehend and write effective reports and design documentation, make effective presentations.

- 11. **Project management and finance:** An ability to apply knowledge, skills, tools, and techniques to project activities to meet the project requirements with the aim of managing project resources properly and achieving the project's objectives.

- *12.* Life-long learning: Recognise the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

### **PROGRAM SPECIFIC OUTCOMES**

**PSO1: Professional Skills:** An ability to apply the knowledge of mathematics, science, engineering fundamentals in ECE to various areas, like Analog & Digital Electronic Systems, Signal & Image Processing, VLSI & Embedded systems, Microwave & Antennas, wired & wireless communication systems etc., in the design and implementation of complex systems.

**PSO2:** Problem-Solving Skills: An ability to solve complex Electronics and communication engineering problems, using latest hardware and software tools, along with significant analytical knowledge in Electronics and Communication Engineering

**PSO3: Employability and Successful career:** Acquire necessary soft skills, aptitude and technical skills to work in the software industry and/or core sector and able to participate and succeed in competitive examinations.

#### List of Experiments:

- 1) Application of Operational Amplifiers

- 2) Design and testing of Active LPF & HPF using op-amp

- 3) Design of Schmitt Trigger using op-amp

- 4) Design of Astable multivibrator using a) op amp b) IC 555

- 5) Line and load regulation of three terminal IC Voltage Regulator.

- 6) Operation of R-2R ladder DAC and flash type ADC

- 7) Simulation of any 4 Experiments 1, 2, 3, 4, 5 and 6 using Multisim software

- 8) Minimization and Realization of a given Function using Basic Gates (AND, OR, NOR, NAND, EXOR).

- 9) Design and implementation of code converters using logic gates (i) BCD to excess-3 code

(ii) Gray to binary

- 10) Design of binary adder and subtractor

- 11) Design and implementation of Multiplexer and De-multiplexer using logic gates.

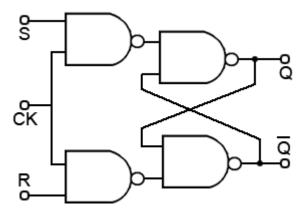

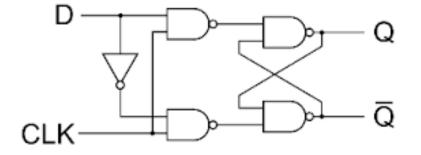

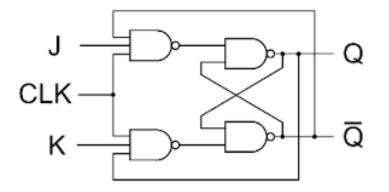

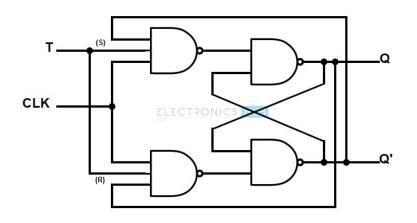

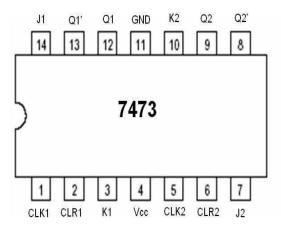

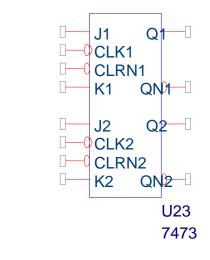

- 12) Implementation and Testing of RS Latch and Flip-flops D, JK and T.

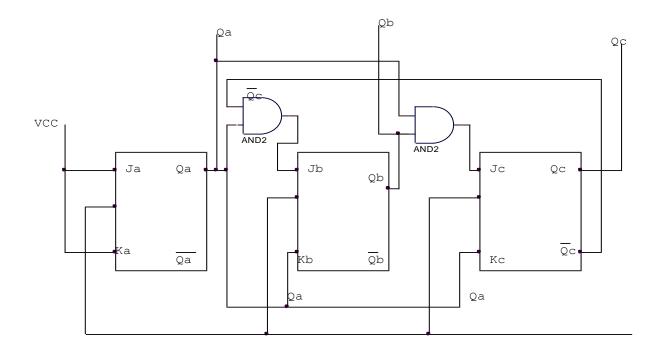

- 13) Design of synchronous counters

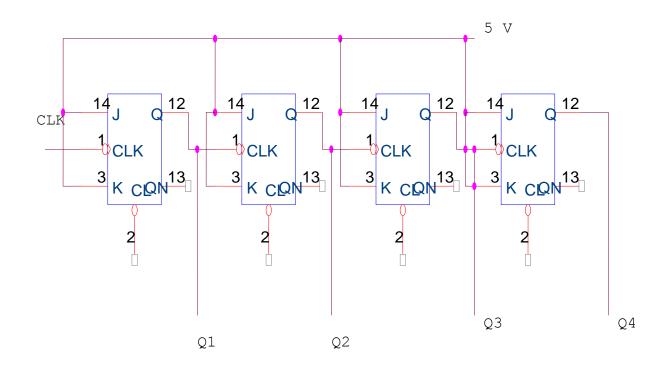

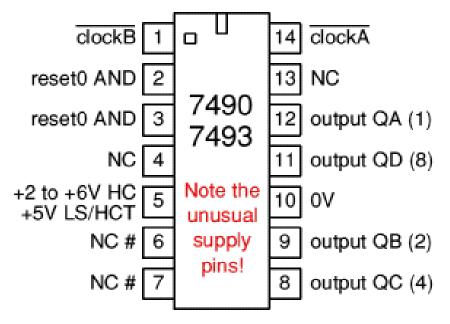

- 14) Design of asynchronous counters

Note: A student has to perform a minimum of 12 experiments.

# **Scheme of Evaluation**

| S.No: | Marks split up                 | Maximum Marks<br>(20) | Marks Obtained |

|-------|--------------------------------|-----------------------|----------------|

| 1     | Preparation of observation     | 5                     |                |

|       | Execution of                   |                       |                |

| 2     | experiment/Results             | 5                     |                |

| 3     | Record                         | 5                     |                |

| 4     | Pre-lab and Post lab questions | 5                     |                |

| 5     | Total                          | 20                    |                |

### **PRECAUTIONS:**

- 1. Wires should be checked for good continuity.

- 2. Carefully note down the readings without any errors.

- 3. While doing the experiment do not exceed the ratings of the IC. This may lead to damage the IC.

# 1. Application of Operational Amplifiers

# Aim:

To realize the following op-amp applications:

(i)Precision Rectifier(ii)Inverting and Non-inverting Comparator(iii)Zero Crossing Detectors

# (i)Precision Rectifier

#### **Pre – Requisites:**

The student should have completed the following study before doing this experiment

- Op-amp theory and characteristics

- Inverting and non-inverting amplifiers

#### **Pre – lab Questions:**

| 1. The rectifying voltage amplita) Tens of voltsb) a fer | <b>A</b>                                   | ctifier is typically<br>a <b>few mill volts</b> | d) microvolt's                   |

|----------------------------------------------------------|--------------------------------------------|-------------------------------------------------|----------------------------------|

| 2. The precision rectifier achiev                        | ves functionality due t                    | 0                                               |                                  |

| a) High input impedance                                  | b) high CM                                 | RR                                              |                                  |

| c) Low output impedance                                  | d) high ope                                | n loop gain                                     |                                  |

| 3. The most important element a) Feedback resistor       | in the precision rectif<br><b>b) diode</b> | ier, apart from op-am                           | p is                             |

| c) input resistor divider                                | d) feedback capacito                       | or                                              |                                  |

| 4. The important requirement o assumed to have           | f the additional comp                      | onent as in question (2                         | 3) above, is that the element is |

| a) Ideal behavior                                        | b) linear op                               | eration                                         |                                  |

| c) Non-linear operation                                  | d) piece-wise linear                       | operation                                       |                                  |

| 5. To minimize the response tim                          | ne and to improve the                      | operating frequency                             | requires the use of              |

| a) Diode                                                 | b) two diod                                |                                                 | -                                |

c) Diode with battery in series d) diode with battery in shunt

#### **Equipment required:**

| Equipment                   | Range/Type             | Purpose                             |  |

|-----------------------------|------------------------|-------------------------------------|--|

| Dual regulated Power supply | <u>+</u> 12V           | For biasing the device              |  |

| Function generator          | 1 MHz                  | To provide input                    |  |

| Oscilloscope                | 20 MHz dual<br>channel | To observe and measure input/output |  |

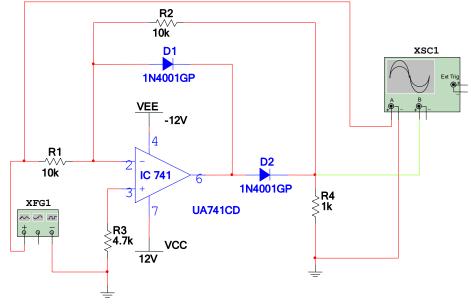

#### Components of the circuit and their purpose:

| Component   | Specification | Quantity | Purpose               |  |

|-------------|---------------|----------|-----------------------|--|

| Op-amp      | IC741         | 1        | Amplification         |  |

| Diode       | 1N4007        | 2        | Rectification         |  |

| Resistor R1 | 10kΩ          | 1        | input resistor        |  |

| Resistor R2 | 10 kΩ         | 1        | feedback resistor     |  |

| Resistor R3 | 4.7 kΩ        | 1        | Compensation resistor |  |

| Resistor R4 | 1 kΩ          | 1        | Load                  |  |

### Theory:

- Precision rectifiers are circuits that rectify voltages below the level of cut-in voltage of the diode.

- The circuit uses op-amp in inverting mode and diode in the feedback path.

- It is used in Half wave rectifiers, Full wave rectifiers, peak value detector, clippers and clampers.

#### **Procedure:**

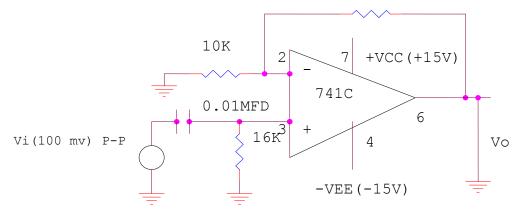

- 1. Construct the circuit as shown in figure

- 2. Set the function generator in sine wave mode and apply 100mV peak-to-peak, 1KHz signal to the input and observe the waveform using oscilloscope.

- 3. Observe the amplifier output waveform using oscilloscope.

#### **Circuit Diagram:**

# **Understanding:**

- The circuit rectifies signal below the cut-in voltage of diode.

- The circuit operates in first quadrant with Vo>0.

- Negative output can be obtained by connecting diode in reverse direction.

#### **Post – lab Questions:**

- a) Half wave rectifier b) full wave rectifier

- c) Peak value detector d) all of the above

2. Precision rectifiers are called so because rectifying voltages are \_\_\_\_\_ of the diode. a) >Vcut-in b) <Vcut-in c) >V<sub>F</sub> d) <V<sub>BD</sub>

| 3. The diode used in the precision rectifier circuit is connected |                         |  |  |  |  |

|-------------------------------------------------------------------|-------------------------|--|--|--|--|

| a) At the input                                                   | b) series with output   |  |  |  |  |

| c) In the feedback path                                           | d) in shunt with output |  |  |  |  |

4. Precision rectifiers could also be used ina) Clipper circuits b) resonance circuits c) voltage doubler d) zero voltage detector

| 5. To obtain negative polarity at the output |                                 |

|----------------------------------------------|---------------------------------|

| a) Input voltage polarity is reversed        | b) diode connection is reversed |

| c) a capacitor is used in feedback path      | d) capacitive load is used      |

# (ii)Inverting and Non-inverting Comparator

#### **Pre – Requisites:**

The student should have completed the following study before doing this experiment

- Ideal characteristics of an op-amp

- Open-loop configuration of op-amp

#### **Pre – lab Questions:**

| 1. | The op-amp in voltage     | comparator operates in        | mode.                 |                |

|----|---------------------------|-------------------------------|-----------------------|----------------|

|    | a) Inverting b) non-      | -inverting                    | c) differential       | d) summing     |

|    |                           |                               |                       |                |

| 2. | The op-amp employed       | in voltage comparator i       | s in config           | uration.       |

|    | a) Positive feedback      | b) negative feedback          | c) open-loop          | d) closed loop |

|    |                           |                               |                       |                |

| 3. | If the bias voltage to th | e op-amp is $\pm 20V$ , the o | output swings between |                |

|    | a) +20V and -20V          | b) 0V and - 20                | )V                    |                |

|    | c) +12V and -12V          | d) 0V and +20                 | )V                    |                |

|    |                           |                               |                       |                |

| 4. | The output voltage is n   | ormally clamped using         |                       |                |

|    | a) voltage divider        | b) feedback re                | esistor c) diodes     |                |

|    | d) zener diodes           |                               |                       |                |

|    |                           |                               |                       |                |

- 5. The speed of operation of the comparator depends on

- a) clamping diodes b) gain of op-amp

- c) clamping zener diode d) power supply

#### **Equipment required**

| Equipment                   | Range/Type             | Purpose                                 |

|-----------------------------|------------------------|-----------------------------------------|

| Dual Regulated Power supply | <u>+</u> 12V DC        | For biasing the device                  |

| Regulated power supply      | (0-12V)DC              | Reference voltage                       |

| Oscilloscope                | 20 MHz<br>Dual channel | To observe and measure input and output |

#### Components of the circuit and their purpose

| Component   | Specification | Quantity | Purpose          |

|-------------|---------------|----------|------------------|

| Op-amp      | IC741         | 1        | Switching        |

| Resistor R1 | 10kΩ          | 1        | Current limiting |

| Resistor R2 | 10kΩ          | 1        | Load resistor    |

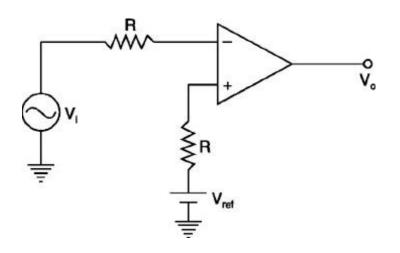

#### **Theory:**

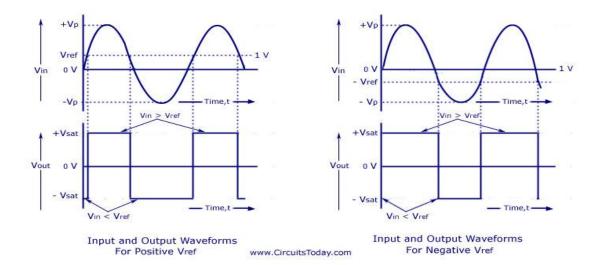

- Voltage comparator is a circuit which compares unknown signal voltage with a known reference voltage.

- Voltage comparator consists of an op-amp operated in open-loop with signal voltage applied at one input and known reference voltage at the other input.

- A fixed reference voltage V<sub>ref</sub> is applied to the inverting terminal and a time varying signal is applied to the non-inverting terminal of the op-amp.

- Op-amp, in open-loop, produces one of the two saturation voltages  $\pm V_{sat}$  at the output.

- When V<sub>ref</sub> is positive, the circuit acts as positive comparator and when V<sub>ref</sub> is negative, the circuit acts as negative comparator.

#### **Procedure:**

- 1. Construct the circuit as shown below in figure

- 2. Set the voltage in V1 to 7V

- 3. Set the reference voltage V2 to +6V.

- 4. Observe simultaneously the input and output waveform using oscilloscope.

Repeat the above steps by changing the reference voltage V2 to - 2V.

#### **Circuit Diagram:**

# **Understanding:**

- In voltage comparator, op-amp operates in open-loop configuration.

- When Vi < Vref, the output is at  $V_{sat}$ .

- When Vi > Vref, the output is at +  $V_{sat}$ .

- By interchanging input and reference voltages, the voltage comparator circuit can be modified as an inverting comparator.

- When  $V_{ref} = 0$ , the circuit becomes a zero crossing detector.

# (iii)Zero Crossing Detector

#### **Prerequisites:**

The student should have completed the following study before doing this experiment

- Ideal characteristics of an op-amp

- Open-loop configuration of op-amp

#### Pre Lab Test:

- In zero crossing detector circuit, the op-amp is used as

a) Inverting amplifier b) non-inverting amplifier c) comparator

d) Schmitt trigger

- A zero crossing detector has a bias voltage of ±10V. When input voltage is positive, the output voltage is

a) +10V

b) 0V

c) -10V

d) +20V

- 3. In general terms, when the input voltage is negative, the output voltage is

a) Equal to input voltage

b) zero

c) Equal to positive bias voltage

d) equal to negative bias voltage

- 4. In a zero crossing detector circuit, the non-inverting input terminal of the op-amp is

a) Connected to the input signal

c) Connected to feedback circuit

b) grounded

d) left open

- 5. The zero crossing detector circuit is similar in operation to

- a) Voltage followerb) integratorc) Schmit triggerd) monostable multivibrator

- 6. The reference voltage for the zero crossing detector is kept at a) +Vcc b)  $-V_{EE}$  c) 0 V d) -Vcc

#### **Equipment required:**

| Equipment                   | Range/Type      | Purpose                      |

|-----------------------------|-----------------|------------------------------|

| Dual Regulated Power supply | <u>+</u> 12V DC | For biasing the device       |

| Oscilloscope                | 20 MHz          | To observe and measure input |

|                             | Dual channel    | and output                   |

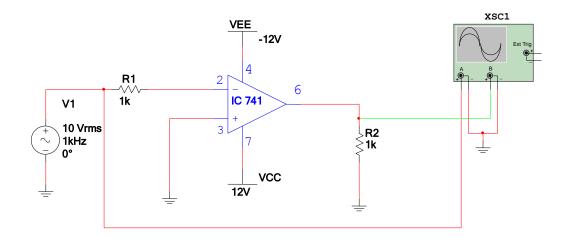

#### Components required and their purpose:

| Component   | Specification | Quantity | Purpose          |

|-------------|---------------|----------|------------------|

| Op-amp      | IC741         | 1        | Switching        |

| Resistor R1 | 1kΩ           | 1        | Current limiting |

| Resistor R2 | 1kΩ           | 1        | Load resistor    |

#### Theory:

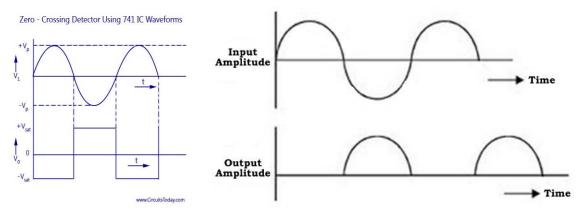

- Zero crossing detectors is a sine wave to square wave converter.

- Zero crossing detector circuit is a comparator with zero reference voltage.

- When the input signal voltage passes through zero in the negative and the positive directions, the output waveform switches between positive and negative saturation levels respectively.

#### **Procedure:**

- 1. Construct the circuit as shown below in figure

- 2. Set the Function Generator in sinusoidal mode at 1 kHz and adjust the amplitude to 6 V peak to peak .

- 3. Observe simultaneously the input and output waveform using oscilloscope.

Repeat the above steps by interchanging the reference voltage and input signal.

#### **Understanding:**

- Zero crossing detector circuit is simply a modified version of voltage comparator with reference voltage as zero.

- In zero crossing detectors, op-amp operates in open-loop configuration.

- When the input voltage crosses zero, the output switches between +  $V_{sat}$  and  $V_{sat}$ .

- Clamping diodes at the input protects the op-amp from damage due to excessive voltage.

- By interchanging input and reference voltages, the circuit can be modified as a noninverting zero crossing detector.

#### **Post Lab Questions:**

- 1. The zero crossing detector output could be controlled using a

- a) Clamping pn junction diode b) capacitor in feedback

- c) Clamping zener diode

- 2. If the frequency f of the sine wave input to the circuit is doubled, the output frequency is a) f/2 b) 2f c) f/4 d) 4f

d) transistor

- 3. If a zero crossing detector has an input of amplitude 15 V and a power supply voltage of ±10V, the Maximum output voltage is

a) +15V b) +25V c) +10V d) +5V

- 4. If the power supply voltage to the zero crossing detector circuit is decreased from ±10V to ±8V, the Minimum output voltage is

a) 0V b) -8V c) -10V d) -18V

- 5. In zero crossing detector circuit, to protect the op-amp from excess voltage at the input, is/are

a) a series capacitor b) a transistor c) a shunt capacitor d) pn ju

d) pn junction diodes

- 6. The speed of operation of zero crossing detector is due to

- a) diode in the feedback pathb) regenerative feedbackc) Zener diode in the feedback pathd) a +ve reference supply

#### **Model Graph**

Used.

#### **RESULT:**

Thus, the use of op-amp as precision rectifier, voltage comparator and zero crossing detector was studied.

# 2. FREQUENCY RESPONSE OF ACTIVE FILTER

### Aim:

To obtain the response of active filters by varying the frequency.

# (i) First Order Low Pass Filter

#### **Pre Requisites:**

The students should have completed the following study before doing the experiment.

- Non inverting op amp.

- Concept of virtual ground in non inverting amplifier.

- Concept of passive filters.

#### **Pre – lab questions:**

| 1. | The desirable feature(s) of filters is/are |

|----|--------------------------------------------|

|----|--------------------------------------------|

| a) Sharp cut-off       | b) Lesser pass band ripple |

|------------------------|----------------------------|

| c) Good phase response | d) All of the above        |

2. The Butterworth filter is characterized by

| a) High gain       | b) Lesser pass band ripple |

|--------------------|----------------------------|

| c) Sharp cut – off | d) All the above           |

3. The circuit arrangement that provides optimal performance in active filter is

| a) Butterworth  | b) Chebyshev |

|-----------------|--------------|

| c) Sallen - Kay | d) Bessel    |

#### 4. An active filter uses

| a) Diode | b) Op-amp |

|----------|-----------|

| c) Zener | d) SCR    |

5. A filter is a circuit that

| a) Provides amplification | b) Removes noise          |

|---------------------------|---------------------------|

| c) Is frequency selective | d) Is an all-pass circuit |

6. The cut off frequency of the low pass filter depends ona) op-amp gainb) feedback resistorc) input resistor

d) RC network

# **Equipment requirement:**

| Equipment          | Range/Type             | Purpose                                 |

|--------------------|------------------------|-----------------------------------------|

| Fixed Power supply | <u>+</u> 12V DC        | To provide operating voltage            |

| Function generator | 1 MHz                  | To provide input signal                 |

| Oscilloscope       | 20 MHz Dual<br>channel | To observe and measure input and output |

# Components required:

| Component   | Specification | Quantity | Purpose          |

|-------------|---------------|----------|------------------|

| Op-amp      | IC741         | 1        | Amplification    |

| Resistor R1 | Potentiometer | 1        | Current limiting |

| Resistor R2 | 10k           | 1        | Load             |

| Resistor R3 | 10k           | 1        | Determines gain  |

| Resistor R4 | 10k           | 1        | Feedback         |

| Capacitor   | 0.01µF        | 1        | Filter element   |

### Theory:

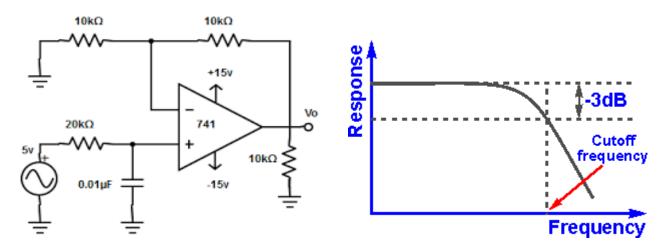

- A filter is a frequency selective circuit that allows only a certain band of frequency components of an input signal to pass through and blocks other frequency components.

- An active filter network is obtained by interconnecting passive elements and active element.

- Op-amp used in active filter also provides amplification.

- A low-pass filter allows only low frequency signals and suppresses high frequency signals.

- The range of frequency varies from dc to cut-off frequency  $f_L$ . The frequency range below cut-off frequency is called *passband* and frequency range beyond  $f_L$  is called *stopband*.

- The gain of the filter

$$\frac{V_o}{V_{in}} = \frac{A_f}{1 + j \left(\frac{f}{F_H}\right)}$$

#### Formula:

Gain,

$$\left| \frac{V_o}{V_{in}} \right| = \frac{A_F}{\sqrt{1 + \left( \frac{f}{f_H} \right)^2}}$$

Phase angle,  $\phi = -\tan^{-1} \left( \frac{f}{f_H} \right)$

#### DESIGN:

#### Design of I order Butter worth filter:

Given the cut off frequency  $F_L$ ,  $A_{O_1}$

$F_L = 1/2\pi RC$

Assume C and then substituting the value in the above formula

Find R, using A<sub>O</sub> and assuming R1 find RF

#### **Design of III order filter**

As the third order filter is a combination of 1<sup>st</sup> order and 2<sup>nd</sup> order Filter, the 2<sup>nd</sup> order can be designed in the same way as the 1<sup>st</sup> Order.

#### **Circuit Diagram**

# **Procedure:**

- 1. Construct the circuit as shown above in figure

- 2. Set the Function Generator in sine wave mode and adjust the amplitude to  $1 V_{peak}$ -peak.

- 3. Observe the waveform using oscilloscope.

- 4. Keeping the input voltage constant at 1V peak-peak, simulate the circuit for frequencies between 10 Hz to 100 kHz.

- 5. Record the amplitude of output voltage for different input frequencies as per table.

- 6. Compute the gain for different frequencies.

# Tabulation

| Input<br>frequency (Hz) | Output voltage,<br>V <sub>o</sub><br>(volts) | Gain =V <sub>o</sub> /V <sub>in</sub> | Gain in dB = $20 \log_{10} V_o/V_{in}$ |

|-------------------------|----------------------------------------------|---------------------------------------|----------------------------------------|

| 10                      |                                              |                                       |                                        |

| 20                      |                                              |                                       |                                        |

| 50                      |                                              |                                       |                                        |

| 100                     |                                              |                                       |                                        |

| 200                     |                                              |                                       |                                        |

| 500                     |                                              |                                       |                                        |

| 1k                      |                                              |                                       |                                        |

| 2k                      |                                              |                                       |                                        |

| 5k                      |                                              |                                       |                                        |

| 10k                     |                                              |                                       |                                        |

| 100k                    |                                              |                                       |                                        |

Input voltage,  $V_{in(PP)} = 1 V$

## **Understanding:**

- Low pass filter allows low frequency signals and suppresses high frequency signals.

- At  $f_L$  the gain falls to  $1/\sqrt{2}$  times the maximum gain.

- The frequency range from dc to  $f_L$  is called the pass band.

- For  $f > f_L$  (stop band) the gain decreases.

- Resistors  $R_3$  and  $R_4$  determine the gain of the filter.

- Gain is high at low frequencies.

- Rate of decay (roll-off rate) is low for first order filter.

- The *roll-off* rate improves with the order of the filter.

### **Post – lab Questions:**

1. As the order of the filter increases,

| a) Sharpness at cutoff improves | b) gain increases               |

|---------------------------------|---------------------------------|

| c) Stop band ripple reduces     | d) pass band ripples are absent |

2. The cut-off frequency of the low pass filter is given by

| a) $f = 2\pi RC$   | b) f = $2\pi/RC$ |

|--------------------|------------------|

| c) $f = 1/2\pi RC$ | d) $f = RC$      |

3. The cut-off frequency of a first order filter with  $R = 1 \text{ K}\Omega$  and  $C = 0.5 \mu\text{F}$  is

| a) 500 Hz | b) <b>330 Hz</b> |

|-----------|------------------|

| c) 533 Hz | d) 300 Hz        |

4. A first order filter with input resistor and feedback resistors of equal values, has Gain of

| a) 1 | b) 10  |

|------|--------|

| c) 2 | d) 0.1 |

5. If the roll-over rate is -20 dB/decade, the addition of another order improves the Roll-over rate to

| a) -10 dB | b) -30 dB |

|-----------|-----------|

| c) -21 dB | d) -40dB  |

6. To construct the second order low pass filter one of the following is required

a) A capacitor in the feedback path

b) another RC section

d) increase the op-amp gain

# (ii) First and Third Order High Pass Filter

#### **Pre Requisites:**

The students should have completed the following study before doing the experiment.

- 1. Non inverting op amp.

- 2. Concept of virtual ground in non inverting amplifier.

- 3. Passive filter concept.

#### **Pre lab Questions:**

- 1. A high pass filter

- a) Allows signals below cut offb) Attenuates signals above cut offd) Allows signals above cut off

- 2. The cut-off frequency of first order high pass filter using R and C is

| a) RC          | b) 1/RC  |

|----------------|----------|

| c) $1/2\pi RC$ | d) 2π/RC |

#### 3. The op-amp in the circuit provides

| a) Filtering | b) Attenuation   |

|--------------|------------------|

| c) Stability | d) Amplification |

#### 4. The voltage gain of the active high pass filter is

| a) 1+R <sub>f</sub> | b) $1 + R_f/R_i$                  |

|---------------------|-----------------------------------|

| c) $R_f/R_i$        | d) R <sub>f</sub> .R <sub>i</sub> |

5. The RC element is connected

| a) At the inverting input | b) At the non-inverting input      |

|---------------------------|------------------------------------|

| c) As feed back           | d) In series with input resistance |

#### 6. The high pass filter could be converted to a low pass filter by

| a) removing the feedback | b) swapping R and C                        |

|--------------------------|--------------------------------------------|

| c) Reduce the gain       | d) connect RC input to the inverting input |

#### **APPARATUS**:

- 1) OP-AMP LM 741C –2

- 2) Resistors  $10k\Omega 4,16 K\Omega 3$

- 3) Capacitors -0.01uf -3,

- 4) Function generator, TRPS, CRO, CRO Probes

- 5) Connecting wires, bread board

#### **Theory:**

- 1. A filter is a frequency selective circuit that allows only a certain band of frequency components of an input signal to pass through and blocks other frequency components.

- 2. An active filter network is obtained by interconnecting passive elements and active element.

- 3. A high-pass filter allows only high frequency signals and suppresses low frequency signals.

- 4. The range of frequency beyond cut-off frequency,  $f_H$  is called *passband* and range of frequency from dc to  $f_H$  is called *stopband*.

- 5. The gain of the filter

$$\frac{V_o}{V_{in}} = \frac{A_f \left( \frac{f}{f_L} \right)}{\sqrt{1 + \left( \frac{f}{f_L} \right)^2}}$$

#### Formula:

$$\frac{V_o}{V_{in}} = \frac{A_f \left( \frac{f}{f_L} \right)}{\sqrt{1 + \left( \frac{f}{f_L} \right)^2}}$$

# **DESIGN: Design of I order Butter worth filter:** Given the cut off frequency $F_L$ , $A_{O,}$ $F_L = 1/2\pi RC$

Assume C and then substituting the value in the above formula

Find R, using A<sub>O</sub> and assuming R1 find RF

#### **Design of III order filter**

As the third order filter is a combination of  $1^{st}$  order and  $2^{nd}$  order Filter, the  $2^{nd}$  order can be designed in the same way as the  $1^{st}$  Order

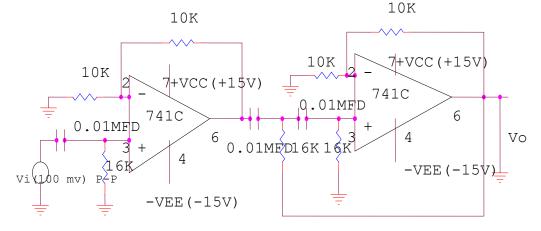

#### **Procedure:**

- 1. Construct the circuit as shown below in figure\_

- 2. Set the Function Generator in sinusoidal mode and adjust the amplitude to  $1 V_{PP}$ .

- 3. Observe the waveform using oscilloscope.

- 4. Keeping the input voltage constant at  $1V_{PP}$ , simulate the circuit for frequencies between 10 Hz to 100 kHz.

- 5. Record the amplitude of output voltage for different input frequencies as per tabulation.

- 6. Compute the gain for different frequencies.

3 rd ORDER HIGH PASS BUTTERWORTH FILTER- Circuit diagram

Table:

| Input frequency<br>(Hz) | Output voltage,<br>V <sub>o</sub><br>(volts) | Gain =V <sub>o</sub> /V <sub>in</sub> | Gain in dB = $20 \log_{10} V_o/V_{in}$ |

|-------------------------|----------------------------------------------|---------------------------------------|----------------------------------------|

| 10                      |                                              |                                       |                                        |

| 20                      |                                              |                                       |                                        |

| 50                      |                                              |                                       |                                        |

| 100                     |                                              |                                       |                                        |

| 200                     |                                              |                                       |                                        |

| 500                     |                                              |                                       |                                        |

| 1k                      |                                              |                                       |                                        |

| 2k                      |                                              |                                       |                                        |

| 5k                      |                                              |                                       |                                        |

| 10k                     |                                              |                                       |                                        |

| 100k                    |                                              |                                       |                                        |

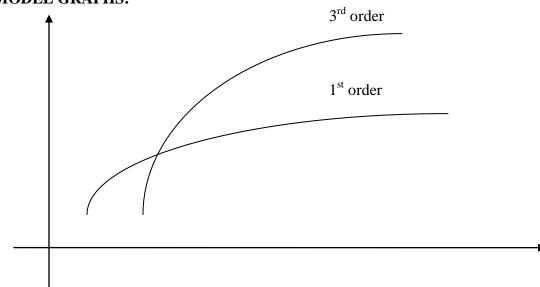

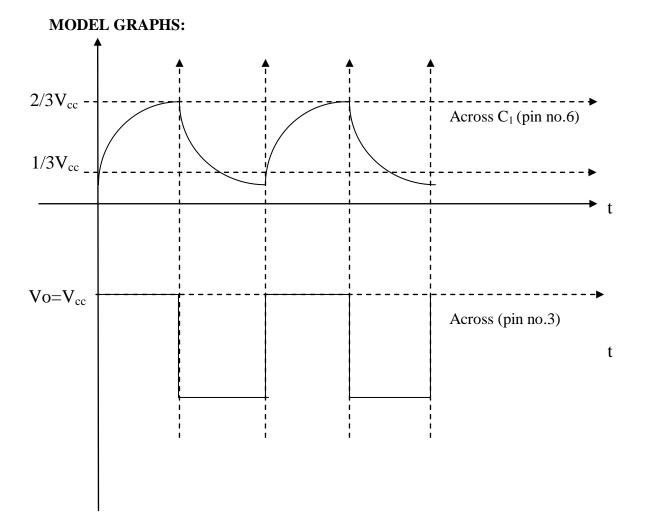

**MODEL GRAPHS:**

### **Understanding:**

- High pass filters allows high frequency signals and stop low frequency signals.

- The frequency range beyond  $f_H$  is called the pass band.

- For  $f < f_H$  (stop band) the gain is lower.

- Resistors R<sub>3</sub> and R<sub>4</sub> determine the gain of the filter.

- High pass filter is dual of low pass filter.

- Maximum gain occurs at high frequencies.

- At low frequencies gain is less.

### **Post – lab Questions:**

1. A first order filter uses  $R_f = 20 \text{ k}\Omega$  and  $R_i = 10 \text{ k}\Omega$ , the gain obtained is

| a) 2 | <b>b</b> ) 3 |

|------|--------------|

| c) 1 | d) 0.5       |

2. The cut-off frequency of the circuit using  $R = 10 \text{ k}\Omega$  and  $C = 0.01 \mu\text{F}$  is

| a) 159 Hz   | b) 159 kHz  |

|-------------|-------------|

| c) 1.59 MHz | d) 1.59 kHz |

3. The gain provided by the circuit using  $R = 10 \text{ k}\Omega$  and  $C = 0.01 \mu\text{F}$  is

| a) 10  | b) 100               |

|--------|----------------------|

| c) 159 | d) insufficient data |

4. In the second order high pass filter

#### a) Another section of RC is used

- b) The positions of R and C is interchanged

- c) An additional RC section is included at the feedback

- d) An RC section is added to the input resistor

- 5. Addition of RC section in higher order filters

| a) Increases ripple | b) Reduces ripple     |

|---------------------|-----------------------|

| c) Improves cut off | d) Provides stability |

6. The value of resistor in the RC network of the filter is doubled, the cut off frequency

a) Doubles

b) is not affected

c) reduces by half

d) reduces by 20%

#### **RESULT:**

The first order low pass and first and third order high pass filters were studied

# **3. SCHMITT TRIGGER**

#### Aim:

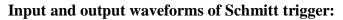

To observe the output waveform of a Schmitt trigger circuit  $V_{HY}$  and to note down the hysteresis voltage  $V_{HY}$  with reference to upper and lower threshold voltages  $V_{UT}$  and  $V_{LT}$  respectively.

### **Pre-Requisites:**

The student should have completed the following study before doing this experiment.

- Resistance divider network

- Op-amp characteristics

- Op-amp configurations

#### **Pre-lab questions:**

1. Schmitt trigger is an example of ----- circuit.

a) Amplifier

b) oscillator

c) switching

d) power supply

| <ul> <li>2. In Schmitt trigger circuit, op-amp switches be</li> <li>a) Cut-off and negative saturation b)</li> <li>c) Slight conduction and cut-off</li> </ul> | etween<br>negative and positive sa<br>d) cut-off and positiv |                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------|

| <ul> <li>3. If the power supply voltage applied to the op±20V, the op-amp saturation voltage is</li> <li>a) 20mV</li> <li>b) 2mV</li> </ul>                    | amp that has a open loop<br>c) 20μV                          | gain of 100db is<br>d) 200µV |

| 4. The operation of a Schmitt trigger is similar to                                                                                                            | o that of a                                                  |                              |

| <ul> <li>a) Full wave rectifier b) series clipper</li> <li>5. The main application of Schmitt trigger is in</li> <li>a) Amplifiers</li> </ul>                  |                                                              | d) clamper                   |

| <ul> <li>a) Amplifiers</li> <li>c) Sine wave to square wave converter</li> </ul>                                                                               |                                                              |                              |

6. The speed of switching in the Schmitt trigger depends ona) Open loop gainb) input resistorc) feedback resistord) hysteresis

# **Equipment Required**

| Equipment            | Range/Type    | Purpose                |

|----------------------|---------------|------------------------|

| Dual Regulated Power | ( 0 – 12V) DC | For biasing the device |

| supply               |               |                        |

| Function generator   | 1 MHz         | To provide input       |

| Oscilloscope         | 20 MHz        | To observe and measure |

|                      | Dual channel  | input/output           |

# Components of the circuit and their purpose

| Components  | Specification | Quantity | Purpose           |

|-------------|---------------|----------|-------------------|

| Op-amp      | IC741         | 1        | Amplification     |

| Resistor R1 | 10kΩ          | 1        | Input resistor    |

| Resistor R2 | 2.2kΩ         | 1        | feedback resistor |

| Resistor R3 | 2.2kΩ         | 1        | feedback resistor |

# **Theory:**

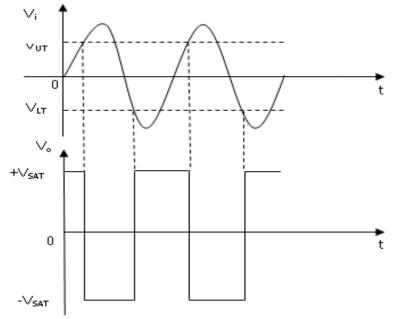

- Schmitt trigger is a comparator with positive feedback.

- It converts sine waveform into square wave.

- The input voltage triggers the output every time it exceeds threshold (upper threshold,  $V_{UT}$  and lower threshold,  $V_{LT}$ ).

- The difference between the two voltage levels,  $V_{UT}$  and  $V_{LT}$ , is hysteresis voltage.

- The Schmitt trigger is also called regenerative comparator.

### **Procedure:**

- 1. Construct the circuit as shown below

- 2. Set the Function Generator in sinusoidal mode and adjust the amplitude to 2 V peak to peak at 1kHz. Observe the waveform using oscilloscope.

- 3. Observe the output waveform using oscilloscope.

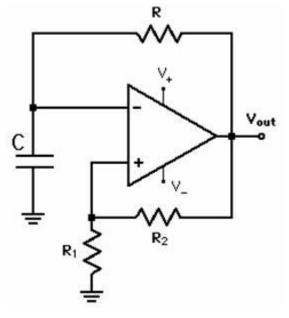

#### **Circuit Diagram**

#### R1=10K $\Omega$ , R2 = R3 = 2.2K $\Omega$

#### **Understanding:**

- Schmitt trigger is a comparator with hysteresis.

- As it compares the input analog waveform with respect to preset values of V<sub>UT</sub> and V<sub>LT</sub>,

Schmitt trigger is also known as two level comparator..

- A non-inverting Schmitt trigger circuit is obtained by interchanging V<sub>i</sub> and V<sub>ref</sub>.

- When an input sinusoidal signal of frequency f is applied, a square wave of same frequency is produced at the output.

- The square wave amplitude is symmetrical about zero level

#### **Calculations:**

Upper threshold voltage:

$$\mathbf{V}_{\mathrm{UT}} = \frac{R_2}{R_1 + R_2} \left( + \mathbf{V}_{\mathrm{SAT}} \right)$$

Lower threshold voltage:

$$\mathbf{V}_{\mathrm{LT}} = \frac{R_2}{R_1 + R_2} \left( -\mathbf{V}_{\mathrm{SAT}} \right)$$

$Hysteres is voltage \quad V_{HY} = V_{UT} - V_{LT}$

Shift angle  $\theta = \operatorname{Sin}^{-1} (V_{\text{UT}}/V_p)$

$V_0$  versus  $V_{in}$  plot or the hysteresis loop of Schmitt trigger:

#### **Post – lab questions:**

- The speed of operation of Schmitt trigger depends on

a) op-amp gain

b) Rate of change of input

c) Supply voltage

d) op-amp configuration

- 2. The switching speed could be improved by using

a) Zener diode at output

b) two Zener diode connected back to back at output

c) Feed back resistor

d) capacitor in feedback

- 3. The Schmitt trigger could be used as

a) Voltage detector

b) astable multivibrator

c) Monostable multivibrator

d) all of the above

- 4. The feedback used in Schmitt trigger is

a) Degenerative

b) regenerative

c) Series

d) shunt

- 5. The value of cross over at increasing or decreasing input are called a) Cut-off points

b) saturation points

c) trip-point

d) null points

- 6. The Schmitt trigger could also be used for

- a) Voltage level detection b) astable operation

- c) Monostable operation d) voltage limiting

#### **RESULT:**

Thus Schmitt trigger was designed and their operation was studied

# 4.(a)Design of Astable multivibrator using op amp

#### Aim:

To design and setup an astable multivibrator using opamp 741,plot the waveforms and measure the frequency of oscillation

### **Pre Requisites:**

The student should have completed the following study before doing this experiment

- 1. Ideal characteristics of an op-amp.

- 2. Concept of inverting and non-inverting amplifiers

- 3. Theory of oscillators

#### **Pre Lab Questions:**

- 1. Astable multivibrator is an example of

- a) Feedback circuit b) Amplifier circuit

- c) Regenerative switch d) bi-stable switch

- 2. The input voltage to astable multivibrator is derived through

- a) Input applied to series resistor at the inverting input

- b) Input applied to series resistor at the non-inverting input

- c) Feedback obtained by voltage divider at the output

### d) Feedback resistor between output and inverting input

3. In astable multivibrator, the capacitor is connected

#### a) Between inverting input and ground

- b) Between non-inverting input and ground

- c) Across feedback resistor

- d) In series with feedback resistor

- 4. The capacitor C charges through the resistor R, towards

- a) Input voltage b) output voltage

- c) Feedback voltage at output voltage divider d) ground voltage

- 5. Square wave output is obtained when 'ON' and 'OFF' times are

- a) Maintained with the ratio 1:2 b) maintained with the ratio 2:1

- c) Maintained with the ratio 1:1 d) maintained with the ratio 1:4

- 6. During both 'ON' and 'OFF' states, the op-amp

- a) Remains at cutoff b) saturates

- c) Swings between saturation and cut off d) conducts slightly

# **Equipments required:**

| Equipment            | Range/Type     | Purpose                      |

|----------------------|----------------|------------------------------|

| Dual Regulated Power | ( 0 – 12V ) DC | For biasing the device       |

| supply               |                |                              |

| Oscilloscope         | 20 MHz         | To observe and measure input |

|                      | Dual channel   | and output                   |

# Components required and their purpose:

| Component       | Specification | Quantity | Purpose          |

|-----------------|---------------|----------|------------------|

| Op-amp          | IC741         | 1        | Amplification    |

| Resistor R1, R2 | 10kΩ          | 2        | Feedback Voltage |

|                 |               |          | divider          |

| Resistor R3     | 4.7kΩ         | 1        | Timing resistor  |

| Capacitor, C1   | 0.1µF         | 1        | Timing capacitor |

## Theory:

- Astable multivibrator is a rectangular wave generator. It is also called free running multivibrator.

- Astable multivibrator toggles between high and low states.

- There are no stable states in astable multivibrator.

- The reference voltage  $V_{ref}$  ( $\beta V_{sat}$  or  $+\beta V_{sat}$ ) is applied to the non-inverting terminal.

- The resistors  $R_1$  and  $R_2$  form a voltage divider network and provide a fraction ( $\beta$ ) of the output to the input as feedback.

- When input at the inverting terminal just exceeds V<sub>ref</sub> switching takes place resulting in rectangular wave output.

- The duration the output remains high, is the time required for the capacitor to charge from  $-\beta V_{sat}$  to  $+\beta V_{sat}$ .

# Formula:

- $T = 2RC \ln (1 + \beta)$  $(1 - \beta)$

- $\beta = R_2/(R_1+R_2)$

• If  $R_1 = 1.16 R_2$ , T=2RC

## **Procedure:**

- 1. Construct the circuit as shown below in figure.

- 2. Observe simultaneously the output waveform and the voltage across the capacitor using oscilloscope.

- 3. Measure the amplitude and frequency.

# **Circuit Diagram:**

$R1 = R2 = 10K\Omega$ ,  $R=4.7K\Omega$ ,  $C = 0.1\mu F$

# Understanding:

- When  $V_o = + V_{sat}$  capacitor charges from  $\beta V_{sat}$  to +  $\beta V_{sat}$  and switches the output  $V_o$  to  $V_{sat}$ .

- When  $V_o = -V_{sat}$  capacitor charges from  $+\beta V_{sat}$  to  $-\beta V_{sat}$  and switches the output  $V_o$  to  $+V_{sat}$ .

- In astable multivibrator, the op-amp operates in the saturation region.

- The output is fed back to the inverting terminal after integrating by a low pass RC combination.

- The duration T is set by external resistor and capacitor..

- The period of the output waveform can be changed by varying R3 or C1.

- The output amplitude can be varied by varying the power supply.

#### **Post Lab Questions:**

- 1. The 'mark' duration of the output is due to

- a) Capacitor charging time

b) capacitor discharging time

c) Capacitor charging upto 1/3 of maximum

d) capacitor charging upto 2/3 of maximum

- 2. The 'space' duration of the output is due to the capacitor

- a) Charging time b) discharging time

- c) Discharging down to 1/3 of maximum d) discharging down to 2/3 of maximum

- 3. The capacitor voltage during 'mark' is proportional to a)  $e^{-tRC}$  b)  $e^{tRC}$  c)  $e^{-t/RC}$  d)  $e^{t/RC}$

- 4. If feedback resistors used at the output are  $R_1$  and  $R_2$ , then the feedback factor,  $\beta$  is given by a)  $R_1 R_2 / R_1 + R_2$  b)  $R_1 / R_1 + R_2$

| a) $\mathbf{K}_1 \mathbf{K}_2 / \mathbf{K}_1 + \mathbf{K}_2$ | $0) \mathbf{K}_{1} / \mathbf{K}_{1} + \mathbf{K}_{2}$ |

|--------------------------------------------------------------|-------------------------------------------------------|

| c) $\mathbf{R}_2 / \mathbf{R}_1 + \mathbf{R}_2$              | d) $R_1 / R_2$                                        |

- 5. If  $V_0$  is the output voltage, then the feedback voltage is given by

- a)  $(R_1 R_2 / R_1 + R_2) V_0$ b)  $(R_1 + R_2) V_0$ c)  $(R_2 / R_1 + R_2) V_0$ d)  $(R_1 / R_1 + R_2) V_0$

- 6. The ON time of the astable multivibrator output is proportional to

- a) Capacitor only b) Resistor only

- c) Both R and C d) input resistor  $R_i$

# 4.(b)Design of Astable multivibrator using IC 555

#### Aim:

To obtain a symmetric square wave output by maintaining certain duty cycle by using 555 timers

#### **Pre – Requisites:**

The student should have completed the following study before doing this experiment

- Functional blocks of 555 timer

- Concepts of capacitor charging and discharging

- Basics of voltage divider networks

#### **Pre – lab Questions:**

1) The astable multivibrator has \_\_\_\_\_ stable states

| a) One  | b) Two           |

|---------|------------------|

| c) Zero | d) Complementary |

2) The main application of astable circuit is in

| a) Gates  | b) Adders   |

|-----------|-------------|

| c) Clocks | d) Memories |

#### 3) The astable circuit requires the following external components:

| a) Capacitor and resistor | b) Capacitors only       |

|---------------------------|--------------------------|

| c) Capacitor and inductor | d) Inductor and resistor |

4) When the duration of the ON and OFF states are equal, the output waveform is

| a) Triangular | b) Rectangular |

|---------------|----------------|

| c) Sinusoidal | d) Square      |

5) To achieve symmetry of the output waveform, the duration of two states of astable multivibrator should be in the ratio

| a) 1 : 2 | b) 2:1   |

|----------|----------|

| c) 1 : 1 | d) 1 : 3 |

- 6. The capacitor in the astable circuit charges towards Vcc through

- a) R1 only b) R2 only c) R1 and R2 d) R1, R2 and ground

- 7. The capacitor discharges towards 0V, through

a) R1 only **b) R2 only** c) R1 and R2 d) R1, R2 and ground

# **Equipment required:**

| Equipment                      | Range/Type          | Purpose                                 |

|--------------------------------|---------------------|-----------------------------------------|

| Dual Regulated Power<br>supply | ( 0 – 12V ) DC      | Biasing the device                      |

| Oscilloscope                   | 20 MHz Dual channel | To observe and measure input and output |

## **Components Required:**

| Component       | Specification | Quantity | Purpose          |

|-----------------|---------------|----------|------------------|

| IC              | 555           | 1        | Timer            |

| Resistor R1, R2 | 47kΩ, 1kΩ     | 1        | External timing  |

| Resistor R4     | 220Ω          | 1        | Load             |

| Capacitor, C1   | 10 μF         | 1        | External timing  |

| Capacitor, C2   | 0.01 μF       | 1        | To bypass ripple |

### **Theory:**

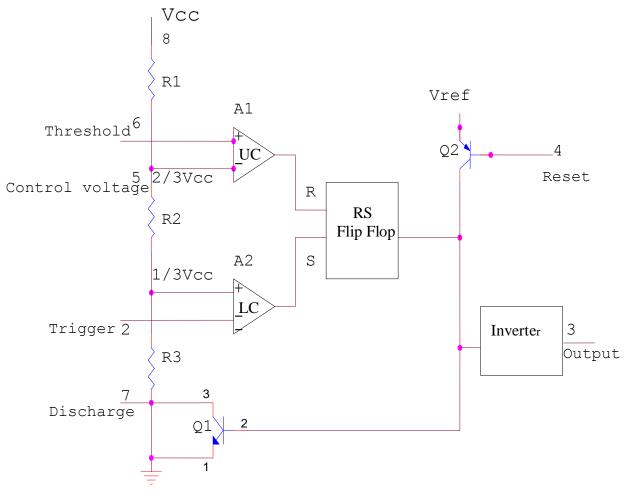

- 555 timer is a device used for generating oscillation or introducing time delay.

- Astable multivibrator is a square wave generator

- Astable multivibrator toggles between one state and the other without the influence of any external control signal.

- It is also called free running multivibrator.

- The timing resistor is split into two sections, R1 and R2, the junction of which is connected to the discharge pin of 555 timer.

- The interval during which the output remains high is the time required for the capacitor to charge from (1/3)  $V_{CC}$  to (2/3)  $V_{CC}$ .

- The period is given by  $T = 0.69 C (R_1+2R_2)$ .

# Formula:

$T_{ON} = 0.69 C (R_1 + R_2)$

$T_{OFF} = 0.69 C R_2$

Period,  $T = T_{ON} + T_{OFF}$

$Duty \ cycle = 100 \ x \ T_{ON} / (T_{ON +} T_{OFF})$

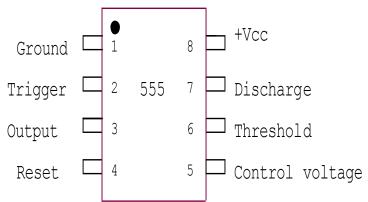

# Internal block diagram of 555 IC

**Pin Diagram**

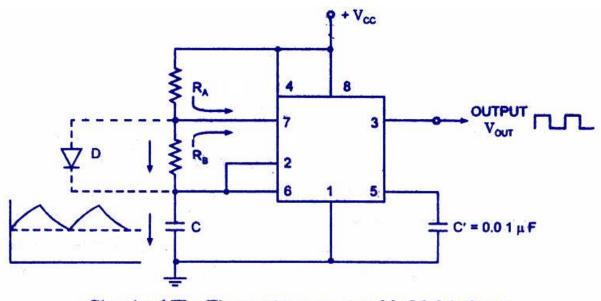

#### **Circuit Diagram**

Circuit of The Timer 555 as an Astable Multivibrator

RA=10KΩ POT, RB=3.3KΩ, C=0.1µF, Vcc =12v

#### **Procedure:**

- Construct the circuit as shown above in figure.

- LED turns ON. After time T<sub>ON</sub>, LED turns OFF.

- Observe simultaneously the output waveform and the voltage across the capacitor, C1, using oscilloscope.

- Measure the period ( $T_{ON}$  and  $T_{OFF}$ ) of output waveform and calculate the duty cycle.

- Repeat the above steps by changing the values of R2 and C1.

#### **Tabulation:**

| S No | $\mathbf{R}_2$ | Theoretical<br>Calculated<br>frequency | Pulse<br>T <sub>ON</sub> | Pulse<br>T <sub>OFF</sub> | Period, T<br>T <sub>ON</sub> + T <sub>OFF</sub> | Frequency,<br>f (1/T) | Duty cycle<br>T <sub>ON</sub> /T |

|------|----------------|----------------------------------------|--------------------------|---------------------------|-------------------------------------------------|-----------------------|----------------------------------|

| 1    | 1kΩ            |                                        |                          |                           |                                                 |                       |                                  |

| 2    | 100 kΩ         |                                        |                          |                           |                                                 |                       |                                  |

| 3    | 1 MΩ           |                                        |                          |                           |                                                 |                       |                                  |

#### **Understanding:**

- When capacitor voltage,  $V_C$ , increases above 2/3  $V_{CC}$ , the output  $V_{out}$  is low and when it is below 1/3  $V_{CC}$ , the output  $V_{out}$  becomes  $V_{CC}$ .

- The waveform across capacitor shows charging and discharging through RC network.

- Astable multivibrator generates square wave.

- The duration, T, is determined by external resistor and capacitor.

#### **Post – lab Questions:**

1. When the astable multivibrator is 'ON', the capacitor

| a) Discharges           | b) Charges |

|-------------------------|------------|

| c) Voltage remains same | d) Is open |

2. The capacitor charges towards  $V_{CC}$

| a) Directly          | b) Through trigger input    |

|----------------------|-----------------------------|

| c) Through resistors | d) Through control terminal |

3. The charging time, in terms of the components is given by

| a) $T = 0.69 (R_1 + R_2)$ | <b>b</b> ) <b>T</b> = <b>0.69</b> ( $\mathbf{R}_1 + \mathbf{R}_2$ ) <b>C</b> <sub>1</sub> |

|---------------------------|-------------------------------------------------------------------------------------------|

| c) $T = 1.1 (R_1 + R_2)$  | d) $T = 1.1$ ( $R_1 + R_2$ ) $C_1$                                                        |

4. The discharge time of capacitor in terms of the components is given by

| a) $T = 1.1 R_2 C_1$  | b) T =1.1 $R_1 R_2 C_1$                                  |

|-----------------------|----------------------------------------------------------|

| c) $T = 0.69 R_2 C_1$ | d) T = 0.69 R <sub>1</sub> R <sub>2</sub> C <sub>1</sub> |

5. The frequency of oscillation of the output waveform is given by

| a) $0.69/(R_1 + 2R_2)C_1$ | b) $1.44/(R_1+2R_2)C_1$    |

|---------------------------|----------------------------|

| c) $0.69/(R_1+R_2)C_1$    | d) $1.44 / (R_1 + R_2)C_1$ |

6. A square wave output is obtained in the astable multivibrator with resistors R1 and R2 in the dRatio

a) 1:1 b) 1:2 c) **2:1** d) 1:3

7. In a 555IC based astable multivibrator circuit if resistors (RA + 2RB) and capacitor C are in the Ratio 1000:1, the frequency of oscillations is given by

a) 6.9 kHz b) 1.44 MHz c) **1.44 kHz** d) 0.69 kHz

8. The duty cycle of a square wave in terms of TON and TOFF is in the ratio

| a) $TON = 2TOFF$ | b) TON = TOFF  |

|------------------|----------------|

| c) 2TON = TOFF   | d) TON = 3TOFF |

#### **RESULT:**

Thus the Astable multivibrator circuit using IC555 and Op-amp(LM 741) were constructed and verified its theoretical and practical time period

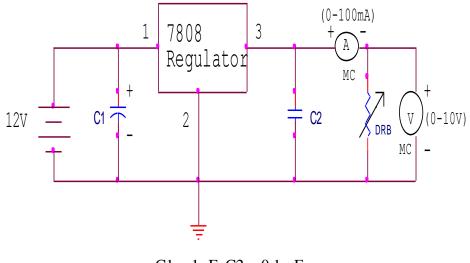

#### 5. IC VOLTAGE REGULATOR

#### Aim:

To obtain the voltage regulation of a 3-terminal fixed IC voltage regulator.

#### **Pre – Requisites:**

The student should have completed the following study before doing this experiment

- Concepts of regulated power supply

- Zener diode as regulator

#### Pre – lab Questions:

- The voltage regulator provides constant dc voltage against variations in

a) Ripple

b) load current

c) input voltage

d) all of the above

- 2. In the series regulator the most important component is thea) Resistorb) capacitorc) dioded)transistor

- The type of diode employed in voltage regulator circuit is usually

a) PN Junction diode

b) Zener diode

c) Tunnel Diode

d) PIN diode

- 4. When a series transistor is used in voltage regulator circuit, it is employed in

a) CE Configuration

b) CB Configuration

c) CC Configuration

d) any of the above configuration

- 5. The terminals of the transistor that are in series with the load (input –output) are

a) base-emitter

b) base-collector

c) collector-emitter

d) emitter-collector

#### 6. A decrease in output voltage in the series voltage regulator leads to

a) Decrease in voltage across zener

#### b) Increase in voltage across base-emitter of transistor

- c) Reduces transistor conduction

- d) Comparator circuit being idle

- 7. An increase in output voltage is sensed by

- a) Sampling circuit b) comparator circuit

- c) Transistor collector-emitter circuit d) zener diode

#### **Equipment required:**

- 1) Ammeter (0-100) mA

- 2) Voltmeter (0-10) V

- 3) Capacitor 1 $\mu$ F, 0.1  $\mu$ F

- 4) Voltage regulator 7808

- 5) Decade resistance box (DRB)

- 6) TRPS

- 7) Bread board

- 8) Connecting wires.

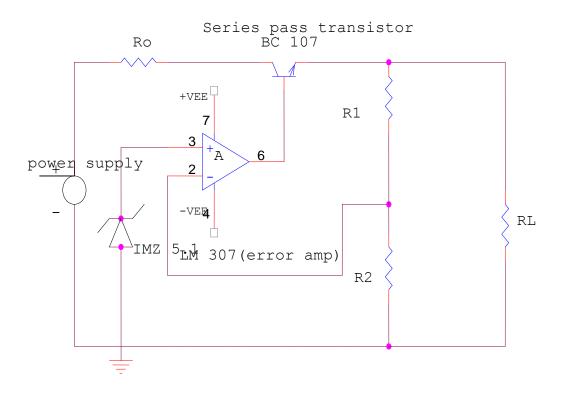

#### **Theory:**

- Voltage regulator is a circuit that maintains the output voltage of power supply constant against the variations of input voltage and changes of load current.

- Zener diode in reverse bias mode is employed as regulator.

- Zener voltage at breakdown region remains almost constant irrespective of the current through it.

- Transistor Q1 is a series pass element which functions as an emitter follower and Q2 functions as voltage comparator and dc amplifier.

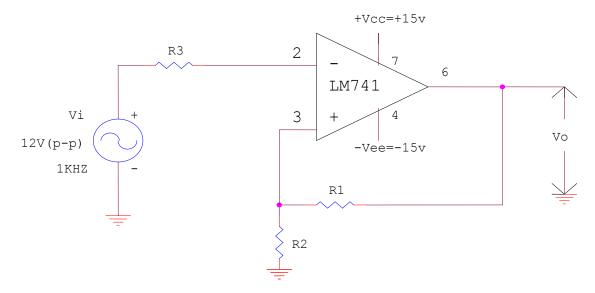

#### **Circuit Diagram:**

3-Terminal Fixed Voltage Regulator

$C1 = 1\mu F, C2 = 0.1 \ \mu F$

#### Tabular form:

#### Table 1:

| S.No | Vin (Volts) | V <sub>NL</sub> (Volts) |

|------|-------------|-------------------------|

|      |             |                         |

|      |             |                         |

|      |             |                         |

#### Table 1:

$V_{NL} =$

| $R_{L(\Omega)}$ | I (mA) | V (Volts) | % Regulation |

|-----------------|--------|-----------|--------------|

|                 |        |           |              |

|                 |        |           |              |

|                 |        |           |              |

#### **Procedure:**

- 1. Connections are made as per the circuit diagram.

- 2. By adjusting the Voltage across RPS to 12V, the load terminals open circuited, the voltmeter reading is noted. This gives the no load voltage.

- 3. The load is varied from  $10K\Omega$  to  $50\Omega$  with the help of decade resistance box the corresponding voltmeter and ammeter reading are noted.

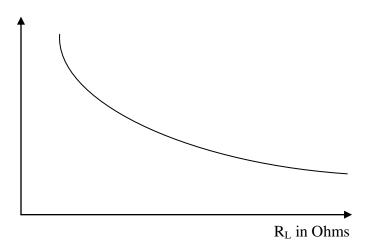

- 4. A graph is drawn between % voltage regulation on y-axis and load resistance on x-axis.

% voltage Regulation = <sup>VNL-Vl</sup>/<sub>VL</sub> × 100

#### **Understanding:**

- Output voltage is constant irrespective of change in supply voltage and load current.

- Series regulators are used in high current and high voltage circuits, whereas shunt regulators are used in low voltage and low current circuits.

#### **Model Graph:**

% Regulation

#### **Post – lab Questions:**

1. The reference voltage required for the series regulator is provided by

- c) Sampling circuit d) transistor emitter

- 2. The feedback section of a series regulator consists of

- a) Comparatorb) sampling circuitc) Control circuitd) all of the above

3. The current limiting in series voltage regulator is provided by using

| a) An additional transistor | b) Op-Amp |

|-----------------------------|-----------|

|-----------------------------|-----------|

c) voltage-divider resistor network d) all of the above

4. The line and load regulation in series voltage regulator may be improved by using

| a) An additional transistor  | b) Op-Amp           |

|------------------------------|---------------------|

| c) an additional zener diode | d) all of the above |

- 5. The additional features that could be incorporated in a series regulator include

a) Current limiting circuit

b) foldback current limiting

c) Over voltage protection

d) all of the above

- 6. Assuming a Zener voltage of 12 V, if the applied input voltage to the series voltage regulator is 20V, the voltage across collector-emitter of the transistor is

a) 8V b) 11.3V c) 7.3V d) 11V

#### **RESULT:**

Thus the voltage regulation of a 3-terminal fixed IC voltage regulator was verified

#### 6. Operation of R-2R ladder DAC and flash type ADC

Aim:

To study the operation of i) R-2R DAC ii)Flash type ADC

#### **APPARATUS REQUIRED:**

| S.NO | APPARATUS        | RANGE            | QUANTITY |

|------|------------------|------------------|----------|

| 1)   | IC               | μΑ741            | 1        |

| 2)   | Resistor         | $1K\Box, 2K\Box$ | 1        |

| 4)   | Multimeter       | •                | 1        |

| 5)   | RPS              | DUAL(0-30) V     | 1        |

| 6)   | Connecting Wires |                  |          |

#### **Pre Lab Questions:**

1. The D-A (ladder network) converter requires

a) Resistor network only

b) Resistor network and active element only

#### c) Resistor network, active element and reference voltage

d) Active element and reference voltage only

2. The ratio of resistances in each section of the resistive network is

a) 1:1 b) 1:2 c) 2:1 d) 1:10

3. For a n-bit conversion, the number of resistor sections required are

a) n b) 2n c) n/2 d)  $n^2$

4. A 10-bit DAC provides voltage resolution between

| a) Vref / 2 <sup>10</sup> | b) Vref x $2^{10}$ | c) Vref x $(2^{10}-1)$ | d) verf x $2^{(10-1)}$ |

|---------------------------|--------------------|------------------------|------------------------|

|---------------------------|--------------------|------------------------|------------------------|

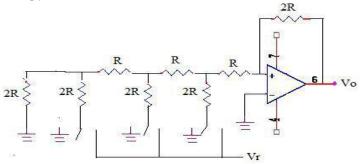

#### **THEORY:**

In weighted resistor type DAC, op-amp is used to produce a weighted sum of digital inputs where weights are produced to weights of bit positions of inputs. Each input is amplified by a factor equal to ratio of feed back resistance to input resistance to which it is connected.

$V_{OUT} = -R_{F/} /R (D_3 + 1/2 D_2 + \frac{1}{4} D_1 + 1/8 D_0)$ 2R ladder type DAC uses resistor of only two values 1

The R-2R ladder type DAC uses resistor of only two values R and2R.The inputs to resistor network may be applied through digitally connected switches or from output pins of a counter. The analogue output will be maximum, when all inputs are of logic high.

$V = -R_{f}/R (1/2 D_{3} + 1/4 D_{2} + 1/8 D_{1} + 1/16 D_{0})$

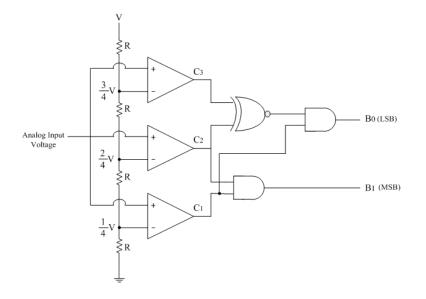

In a 3 input ADC, if the analog signal exceeds the reference signal, comparator turns on. If all comparators are off, analog input will be between 0 and V/4.If C1 is high and C2 is low input will be between V/4 andV/2.If C1 andC2 are high and C3 is low input will be between 3V/4 and V.

#### **PROCEDURE:**

- 1. Connect the circuit as shown in circuit diagram.

- 2. For various inputs, measure the outputs using multimeter.

#### **CIRCUIT DIAGRAM:**

a) R-2R Ladder DAC:

R=1KΩ Input and Output Table:

| S.No. | D2 | D1 | D0 | Vth  | Vprac |

|-------|----|----|----|------|-------|

| 1)    | 0  | 0  | 0  | 0    | 0     |

| 2)    | 0  | 0  | 1  | 1.25 | 1.3   |

| 3)    | 0  | 1  | 0  | 2.5  | 2.7   |

| 4)    | 0  | 1  | 1  | 3.75 | 3.5   |

| 5)    | 1  | 0  | 0  | 5    | 4.9   |

| 6)    | 1  | 0  | 1  | 6.25 | 6.5   |

| 7)    | 1  | 1  | 0  | 7.5  | 7.2   |

| 8)    | 1  | 1  | 1  | 8.75 | 8.3   |

#### 2 Bit Flash Type ADC

#### Input and Output Table:

| Analog Input                                                                                                | Comparator Outputs |    |       | Digital output |                |

|-------------------------------------------------------------------------------------------------------------|--------------------|----|-------|----------------|----------------|

| Conditions                                                                                                  | C1                 | C2 | $C_3$ | $B_1$          | B <sub>0</sub> |

| $0 ~\leqslant~ V_{in} ~\leqslant~ \frac{V}{4}$                                                              | 0                  | 0  | 0     | 0              | 0              |

| $\frac{V}{4} \ \leqslant \ V_{in} \ \leqslant \ \frac{2V}{4}$                                               | 1                  | 0  | 0     | 0              | 1              |

| $\frac{2V}{4} ~\leqslant~ V_{in} ~\leqslant~ \frac{3V}{4}$                                                  | 1                  | 1  | 0     | 1              | 0              |

| $\frac{3V}{4} \hspace{0.1 in} \leqslant \hspace{0.1 in} V_{in} \hspace{0.1 in} \leqslant \hspace{0.1 in} V$ | 1                  | 1  | 1     | 1              | 1              |

#### Post Lab Questions (Part A)

## **1.** How many comparisons will be performed in an 8 bit successive approximation type ADC?

8 Comparisons

## 2. The basic step of 9 bit DAC is 10.3mV. If 000000000 represents 0V. What output is produced if the input is 101101111?

7.38mV.

#### 3. State the applications of DAC and ADC .

- a) Digital signal processing

- b) Communication circuits

## 4. For R-2R ladder 4 bit type DAC find the output voltage if digital input is 1111. Assume VR = 10V, R = Rf = 10K.

Vo = 9.375V

#### 5. Which is the fastest type of ADC? Why?

Successive approximation is the fastest type of ADC. It completes n-bit conversion in n clock periods.

#### Post Lab Questions: (Part b)

1. If the reference voltage is 10V in a 4-bit resistive network, the output voltage for digital input '1001' is

**a**) **5.625 V b**) 9 V **c**) 5 V **d**) 9.375 V

2. If the reference voltage is 10V, the resolution of the 4-bit D-A converter is

a) 1 V b) 5 V c) **0.625 V** d) 0.5 V

3. A 10-bit DAC as above, uses 10V reference, the output voltage would be approximately in steps of

a) 1024mV b) 10mV c) 100mV d) 1V

4. In the binary ladder circuit, the number of resistors required for n-bit realization is

a) nR b) 2nR c) (2nR)-1 d) (2nR)+1

5. The effective resistance, looking either backward or forward from any of the nodes in a binary ladder network is

6. If the input to a binary ladder circuit is '1000' and the reference voltage is 'V' volts, the output voltage is equal to

a) V b) 2V c) V/2 d) 8V

7. An additional circuit that is required at each input node is

a) Comparator **b) register** c) level amplifier d) AND gate

**RESULT:**

The operation of R-2R ladder DAC and Flash type ADC was studied

# 8. Minimization and Realization of a given Function using Basic Gates (AND, OR, NOR, NAND, EXOR).

#### AIM:

- (ii) To verify the truth tables of all logic gates.

- (ii) To Realize the Given Function Using Basic Gates  $\Gamma$  (iii)  $\Gamma$

- F (w, x, y, z) =  $\sum (0,1,2,3,4,5,6,9,10,11,12,13)$

#### **APPARATUS:**

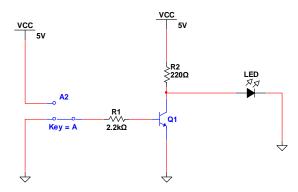

- i) IC 74LS04 (NOT Gate)

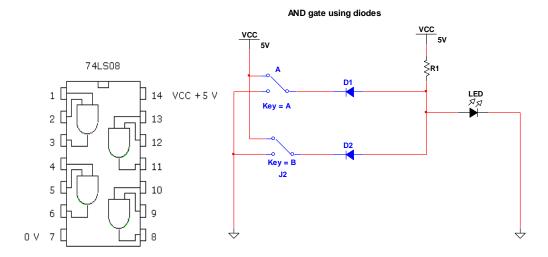

- ii) IC 74LS08 (two input AND gate)

- iii) IC 74LS32 (two input OR gate)

- iv) IC 74LS86 (two input EX-OR gate)

- v) IC 74LS00 (two input NAND gate)

- vi) IC 74LS02 (two input NOR gate)

- vii) Digital IC Trainer Kit

- viii) Connecting Wires

#### **Pre – lab Questions:**

- 1. According to De Morgan's first Law, the complement of sum is equal to

- a) `1' b) product of complements

- c) `0' d) sum of complements

- 2. If three inputs A,B and C are used, then according to De Morgan's Law, (A+B+C)' equals

| a) (A+B)'+C' | b) A+(B+C)' |

|--------------|-------------|

| c) A' B' C   | d) A'B'C'   |

3. When same inputs are applied to a 2-input NOR gate, the output obtained is

| a) 1                                                                    | b) complement of input   |  |  |  |

|-------------------------------------------------------------------------|--------------------------|--|--|--|

| c) 0                                                                    | d) same as input         |  |  |  |

| 4. The NOT function is performed using regions of transistor operation. |                          |  |  |  |

| a) Active and cutoff                                                    | b) active and saturation |  |  |  |

| c) Cutoff and saturation                                                | d) saturation            |  |  |  |

5. In a AND gate constructed using diodes, the input is applied to the \_\_\_\_\_ while the output is taken at

the junction of \_\_\_\_\_.a) anode, cathodesc) either (a) or (b)d) none of the above

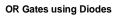

- 6. The diode circuit in a OR-gate configuration

- a) Requires separate power supply

- b) Doesn't require power supply

- c) Always has the diodes turned ON

- d) Always has the diodes turned OFF

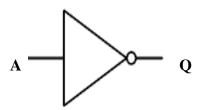

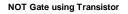

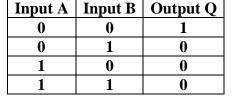

#### NOT GATE:

Symbol:

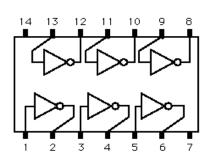

**PINDIAGRAM:**

#### Truth table:

| Input A | Output Q |

|---------|----------|

| 0       | 1        |

| 1       | 0        |

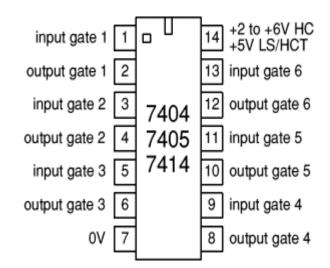

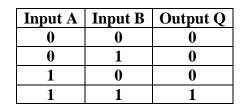

#### TRUTH TABLE:

SYMBOL:

**PIN DIAGRAM:**

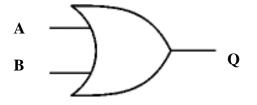

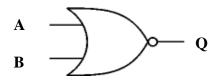

**OR GATE:**

SYMBOL:

**TRUTH TABLE:**

| Input A | Input B | Output Q |

|---------|---------|----------|

| 0       | 0       | 0        |

| 0       | 1       | 1        |

| 1       | 0       | 1        |

| 1       | 1       | 1        |

**PIN DIAGRAM:**

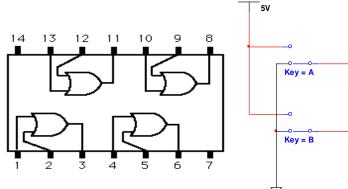

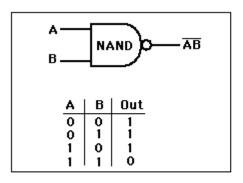

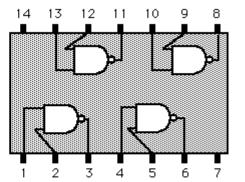

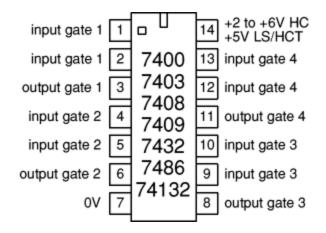

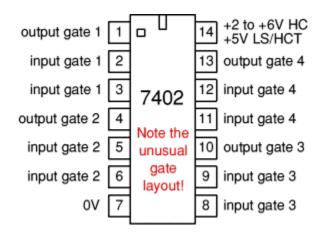

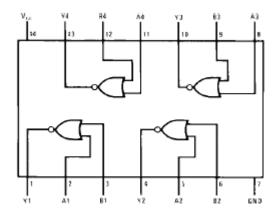

#### NAND GATE:

#### SYMBOL & TRUTH TABLE:

7400 or 74LS00 quad two-input NAND gate.

#### **EXCLUSIVE – OR GATE:**

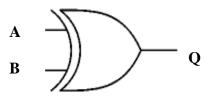

**SYMBOL:**

#### **TRUTH TABLE:**

| Input | Input | Output |

|-------|-------|--------|

| Α     | B     | Q      |

| 0     | 0     | 0      |

| 0     | 1     | 1      |

| 1     | 0     | 1      |

| 1     | 1     | 0      |

#### **PIN DIAGRAM:**

#### SYMBOL:

#### **PIN DIAGRAM:**

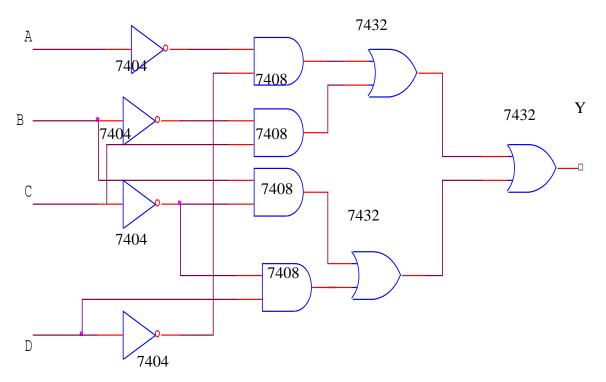

MINIMIZATION

| AB/CD                         | $\mathbf{C}^{!}\mathbf{D}^{!}$ | C'D | CD | CD! |   |

|-------------------------------|--------------------------------|-----|----|-----|---|

| A <sup>!</sup> B <sup>!</sup> | 1                              | 1   | 1  | 1   |   |

| A <sup>!</sup> B              | 1                              | 1   | 0  | 1   |   |

| AB                            | 1                              | -1  | 0  | 0   |   |

| AB <sup>!</sup>               | 0                              | 1   | 1  | 1   |   |

|                               |                                |     |    |     | - |

$$\mathbf{Y} = \mathbf{C}^{\mathbf{I}} \mathbf{D} + \mathbf{C}^{\mathbf{I}} \mathbf{B} + \mathbf{B}^{\mathbf{I}} \mathbf{C} + \mathbf{A}^{\mathbf{I}} \mathbf{D}^{\mathbf{1}}$$

#### **PROCEDURE:**

- 1. The given function minimized using karnaugh maps.

- 2. Implement the logic diagram with truth table

- 3. Verify the Boolean function experimentally basic gates.

- 4. The truth tables are to be verified.

#### **TRUTH TABLE**

#### LOGIC CIRCUIT

Viva Questions:

. What is SOP?

The logical sum of the several product variables is called sum of product. It is basically an OR operation of AND operated variables.

Y=AB+BC+CA

2. What is POS?

The logical product of the several sum variables is called product of sum. It is basically an AND operation of OR operated variables.

Y = (A+B)(B+C)(C+A)

3. State De Morgan's theorem?

The first theorem states that the complement of a product/sum is equal to the sum/product of the complements.

4. What is Minterm?

Product term containing all the possible variables of the function in either complement or uncomplementary form is called Minterm.

5. What is Maxterm?

Sum term containing all the possible variables of the function in either complement or uncomplement form is called Maxterm

**RESULT:** (i)The truth tables of six logic gates were verified (ii)The given functions were realized using basic logic gates and the values of the truth table were

verified.

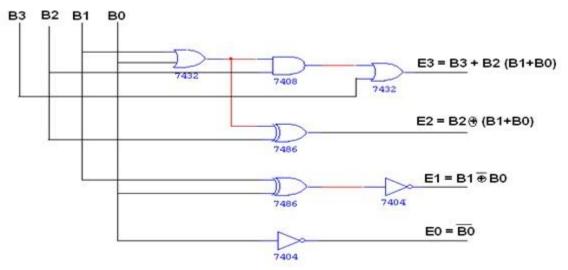

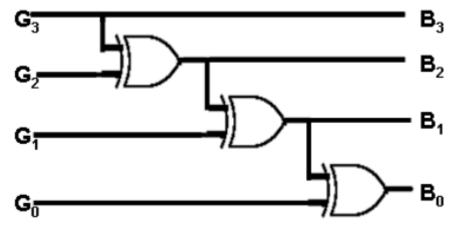

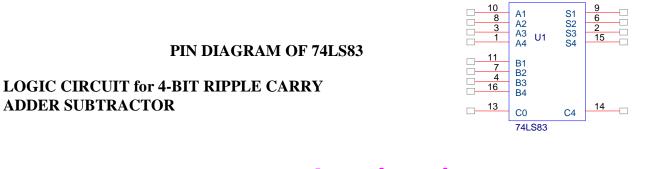

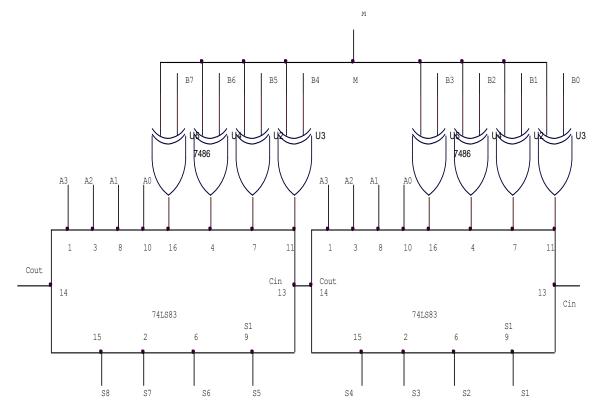

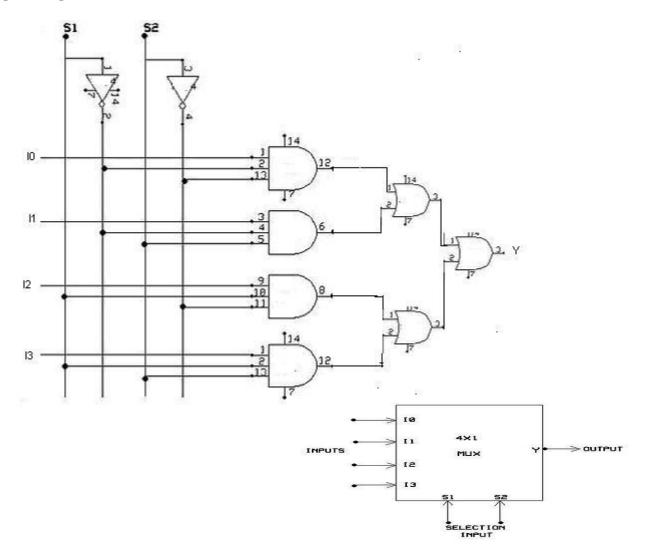

### 9. Design and implementation of code converters using logic gates

### (i) BCD to excess-3 code

#### Aim:

To construct the circuit of BCD to excess-3 code and Gray to Binary and study their working

#### **Pre-lab questions:**

1) BCD stands for

|    | a. binary code                        |                 |                 | b. Binary coded digit |                         |        |

|----|---------------------------------------|-----------------|-----------------|-----------------------|-------------------------|--------|

|    | c. Binary coded decimal               |                 |                 |                       | d. Binary coded display |        |

| 2) | Excess- 3 cod                         | e of a given wo | ord is obtained | by addi               | ng to it                |        |

|    | 3 bits                                | b. Equivalent   | of decimal 3    |                       | c. '111'                | d. '1' |